エッジ処理に最適化した学習機能付きAIハードウェアの開発

エッジコンピューティング向けの学習機能を持つAI技術の革新

東京理科大学の研究チームが、エッジでの学習機能を備えた新しい人工知能技術、三値勾配二値化ニューラルネットワーク(TGBNN)を提案しました。TGBNNは、勾配を3値で扱うことで、エッジ環境でも重みの更新を維持しつつ、低消費電力での計算を可能にします。また、スピントロニクス技術を駆使し、単一MRAMセルを利用した新たな演算手法を考案。これにより、AIやIoT時代に適応した省エネ性能を持つ学習機能を持つAIが実現されます。

この記事の要約

- 新たに提案されたTGBNN技術がエッジでの学習機能を可能にする。

- スピントロニクス技術を活用したMRAMアレイの利用が実現された。

- AIやIoTにおけるコンピューティングリソースの効率化が期待される。

【研究の要旨とポイント】

エッジでの“学習機能”を備えた人工知能の実現に向け、エッジでの演算の回路規模、消費電力を可能な限り抑えることが求められており、そのためには、重み及び活性化値を2値で扱うBinarized neural network (BNN) の適用が必須となります。

しかし、従来のBNNでは、推論時は重み及び活性化値を2値とできるものの、学習時はいずれも実数なので、ほとんどの計算が実数計算となるため、BNNによる人工知能の“学習機能”をエッジ側に持たせることは難しいという課題がありました。

今回、学習時に利用する勾配に3値を採用して重みの更新は2値のまま行えるBNNである三値勾配二値化ニューラルネットワーク(TGBNN: Ternary gradients binarized neural network)を提案し、スピントロニクス技術を活用したMRAMアレイを用いることで、TGBNN実現に先鞭をつけました。

本手法を適用することで、学習機能を備えたままBNNをエッジでも実現することが可能になると期待されます。

【研究の概要】

東京理科大学工学部電気工学科の河原 尊之教授と同大学大学院工学研究科電気工学専攻の藤原 優哉氏(2023年度修士課程修了)は、学習時に利用する勾配に3値を採用して重みの更新は2値のまま行うことができるBNNである三値勾配二値化ニューラルネットワーク(TGBNN: Ternary gradients binarized neural network)を提案しました。更に、スピントロニクス(*1)技術を活用し、単一MRAM(磁気抵抗メモリ、*2)セルによるXNOR ゲート及び確率的更新手法を考案しました。これをメモリ素子と演算素子を1つのチップ上で統合したComputing in Memory (CiM) として利用したMRAMアレイを用いることで、TGBNN実現の先鞭をつけました。

人工知能(AI)やIoT(Internet of things)に普及に伴い、コンピューティングリソースの増大が社会問題となりつつあります。そのため、エッジでの“学習機能”を備えた人工知能の実現が望まれており、回路規模、消費電力を抑えたエッジでの演算処理技術の開発は急務です。

この背景から、①重み及び活性化値を最小である1ビットとしてしまう、すなわち“–1”, “+1”の2値で扱うBinarized neural network (BNN) の適用、②メモリ素子と演算素子を1つのチップ上で統合させるComputing in Memory (CiM)を用いた実装、を両輪とした技術の発展が重要となります。

しかしながら、従来のBNNでは、推論時は重み及び活性化値を2値とできるものの、学習においてはいずれも実数であることから、ほとんどの計算が実数計算となります。このため、BNNによる人工知能の“学習機能”をエッジ側に持たせることは難しいというのが現状です。

そこで今回、学習時に利用する勾配に3値を採用して重みの更新は2値のまま行えるBNNである三値勾配二値化ニューラルネットワーク(TGBNN: Ternary gradients binarized neural network)を提案しました。更に、スピントロニクス技術を活用して単一MRAMセルによるXNOR ゲート及び確率的更新手法を考案しました。これをCiMとして利用したMRAMアレイを用いることで、TGBNN実現の見通しを得ることができました。

また、MNIST データセットを用いて提案手法を評価した結果、88%を超える高い精度が確認でき、応用に向けて大きく前進しました。

本研究成果は、2024年10月8日に国際学術誌「IEEE Access」にオンライン掲載されました。

【研究の背景】

人工ニューラルネットワーク(ANN)は重要な人工知能技術の1つであり、画像処理・ 音声処理・自然言語処理など様々な分野で用いられており、近年、発展が著しい技術です。ANNの高度化は、より複雑な処理を可能にするため、更なる活用が期待されていますが、必要なコンピューティングリソースの増大が課題として挙げられます。

一方、発展が続くInternet of things (IoT) 社会では、ネットワーク負荷の軽減、処理速度・セキュリティ向上が求められており、そのためにはモノ側(エッジ側)での演算処理が必要不可欠となります。そのため、推論のみでなく、その場でのデータに合わせた学習機能も有するANNをエッジ側で実現する技術が求められています。こうしたエッジでの演算を実現するためには、コンピューティングリソースそのものを可能な限り抑える必要があります。

このような背景において、ソフトウェアの観点からはBinarized Neural Network (BNN) 技術が重要となります。BNNは、重みや活性化値が“–1”と“+1”の2値のANNであり、最小の情報単位である1ビットとして扱うことによりコンピューティングリソースを低減できます。一方、ハードウェアの観点からは、Computing in Memory (CiM) 技術の活用が求められます。CiMはメモリ素子と演算素子が1つのチップ上で統合された構造で演算処理を行うという概念で、こちらもコンピューティングリソースの大きな低減が期待されている技術です。

なお、これらの背景、課題、従来技術については、書籍「人工知能チップ回路入門」(河原尊之著、コロナ社)でより詳しく解説していますので、興味のある方はそちらもご参照ください。

【研究結果の詳細】

今回、スピントロニクス技術を活用し、MRAM(磁気抵抗メモリ)を用いたCiMアーキテクチャによるBNNについて新たな手法を提案しました。具体的な提案内容は、以下の3点です。

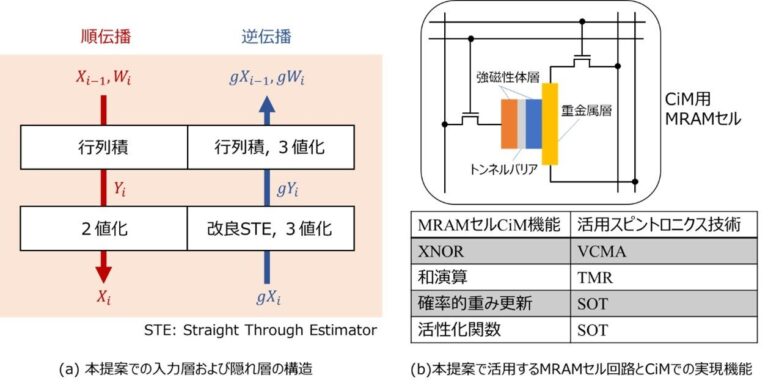

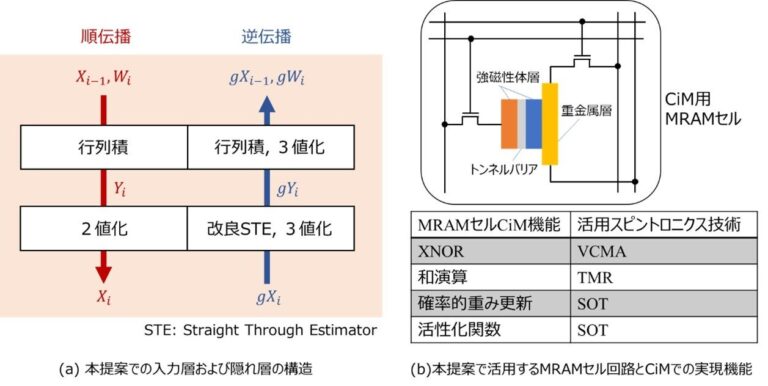

① 3値勾配を⽤いた新たなBNN学習アルゴリズムの提案(図1a)。

3値である “–1”, “0”, “+1” の勾配を用いて、2値である“–1”, “+1”のパラメータを学習させるアルゴリズムであり、Straight through estimator(STE、*3)及びMRAMセルを活用した確率的なパラメータ更新、活性化関数機能実現といった手法を用いました。

② 単一MRAMセルによるXNORゲートの実現およびそれらを利用したMRAMアレイによるBNN学習回路の実現 (図1b)。

MRAMにおける異なる2種類のデータ書き込み方式であるスピン軌道トルク(SOT、*4)と電圧制御磁気異方性(VCMA、*5) を用いて、従来方式よりも積和演算回路の規模を半減させることに成功しました。

③ BNN学習アルゴリズム(①)を提案したMRAMアレイ(②)上で実行する手法を開発。

すなわち、提案したアルゴリズムにより学習演算の軽量化を行い、それを提案したMRAMアレイ上で実行することで、回路規模削減を実現と、性能は保持したままで2段階にてコンピューティングリソースを減らすことに成功しました。そして、MNISTデータセットを用いた学習で提案手法の評価を行った結果、88%を超える精度を確認しました。これらの結果から、今回提案した手法をもちいることで、学習機能を備えたままでエッジでもBNNを実現することが可能となることが期待されます。

【用語】

*1 スピントロニクス

電子は電荷の他にスピン角運動量とよばれる固有の物理量をもつ。この電子スピンに対する学問領域をスピントロニクスという。

*2 MRAM

次世代メモリの1つ。スピントロニクス技術を活用し、不揮発、高速書き込み、低消費電力という特長を持つ。すなわち、TMRと呼ばれる絶縁体薄膜を強磁性体薄膜で挟んだメモリ素子の3層構造で情報を記憶する。更に今回の提案では、実用化への検討が進んでいる4層目として重金属薄膜を備えたメモリ素子を想定した。ここでMRAMのメモリ素子では、自由層と呼ばれる強磁性体薄膜における磁化容易軸での2つの向きを記憶情報として用いる。この向きを反転する(情報を書き換える)には、エネルギーが高い状態を一度通る、すなわちエネルギーの障壁を越える必要がある。この実現方法が、下記のSOTやVCMAである。

*3 Straight through estimator (STE)

BNNは重み及び活性化値が“–1”, “+1”の2値のニューラルネットワーク(NN)のこと。しかしながら、学習時(逆伝播時)には通常のNN同様に実数勾配と実数重みが必要となる。つまり、順伝播時には2値、逆伝播時には実数で動作することとなる。BNNでは活性化関数として符号関数が⽤いられるが、符号関数の微分はほぼ全ての区間で0となるため逆伝播時に勾配が伝播しないため、逆伝播時には符号関数をhard tanh で近似する。これをStraight through estimator (STE) という。本提案では勾配が存在する区間をパラメータとする手法に改良して用いている。

*4 スピン軌道トルク (SOT)

磁性体に電子スピンを注入するときに発生するトルクのこと。SOTによって磁化の方向を制御できるため、MRAMのデータ書き込み方式の1つとして検討されている。重金属薄膜を備えたTMR構造のメモリ素子において、重金属層に電流を流すと、スピンホール効果 (SHE) によって電流とは垂直に純スピン流が誘起される。この純スピン流により、メモリ素子内の強磁性体薄膜の磁化はSOT を受けることとなる。

*5 電圧制御磁気異方性 (VCMA)

磁性体には磁化されやすい⽅向である磁化容易軸(エネルギーが低く安定)と磁化されにくい⽅向である磁化困難軸(エネルギーが高く不安定)が存在する。両者にはエネルギーの障壁があることになる。この障壁の高さが素子に印可された電圧で変化することを言う。エネルギー障壁高さを制御して磁化反転(情報の書き換え)を行う手法としてこのVCMA効果を利用する。

【論文情報】

雑誌名:IEEE Access

論文タイトル:TGBNN: Training Algorithm of Binarized Neural Network with Ternary Gradients for MRAM-based Computing-in-Memory Architecture

著者:Yuya Fujiwara and Takayuki Kawahara

DOI:10.1109/ACCESS.2024.3476417

※本論文はオープンアクセスです。自由にダウンロードし、お読みいだけます。

【発表者】

藤原 優哉 東京理科大学大学院工学研究科電気工学専攻 修士課程2023年度修了 <筆頭著者>

河原 尊之 東京理科大学工学部電気工学科 教授 <責任著者>

【関連国際学会】

学会名:2023 IEEE Region 10 Conference (TENCON 2023)

論文タイトル:BNN Training Algorithm with Ternary Gradients and BNN Based on MRAM Array

著者:Yuya Fujiwara and Takayuki Kawahara

DOI:10.1109/TENCON58879.2023.10322327

発表日:2023年11月1日(水)

【発表者】

藤原 優哉 東京理科大学大学院工学研究科電気工学専攻 修士課程2023年度修了 <筆頭著者>

河原 尊之 東京理科大学工学部電気工学科 教授 <責任著者>

※PR TIMESのシステムでは上付き・下付き文字や特殊文字等を使用できないため、正式な表記と異なる場合がございますのでご留意ください。正式な表記は、東京理科大学WEBページ(https://www.tus.ac.jp/today/archive/20241023_8355.html)をご参照ください。