東北大学、NEC、アイシンが共同開発のAI半導体がCEATEC AWARDで受賞

東北大学とNEC、アイシンがAI半導体でCEATEC AWARD受賞

国立大学法人東北大学、日本電気株式会社(NEC)、株式会社アイシンは、NEDOの技術開発事業に基づく「CMOS/スピントロニクス融合AI半導体」でCEATEC AWARD 2024のネクストジェネレーション部門賞を受賞しました。この半導体は、磁気抵抗メモリ(MRAM)を搭載し、不揮発性と広帯域性を生かしたシステムアーキテクチャを実現。従来と比べて電力効率を10倍以上改善し、起動時間も10分の1以下に短縮することに成功しました。今後はさらに半導体の製品化を進め、実用化を目指していきます。また、成果はCEATEC 2024のNEDOブースで紹介予定です。

この記事の要約

- 東北大学、NEC、アイシンが共同開発した半導体が受賞。

- 電力効率10倍以上、起動時間10分の1以下を実現。

- CEATEC 2024で成果を紹介し、製品化を進める。

NEDOの「省エネAI半導体及びシステムに関する技術開発事業」(以下、本事業)の一環で、「CMOS/スピントロニクス融合技術によるAI処理半導体」の研究開発に取り組む国立大学法人東北大学、日本電気株式会社(NEC)、株式会社アイシンは、その成果である「CMOS/スピントロニクス融合AI半導体」についてイノベーション性が高く優れたものを表彰する「CEATEC AWARD 2024」に応募し、このたび、ネクストジェネレーション部門賞を受賞しました。

今回受賞した「CMOS/スピントロニクス融合AI半導体」は、CMOS/スピントロニクス融合技術である磁気抵抗メモリ(MRAM)を大容量搭載し、その不揮発性と広帯域性を活用したシステムアーキテクチャにより、エッジ領域で動作するAI(人工知能)半導体において今後ますます重要となる、動作時および待機時電力の大幅削減を実現する技術で、システム動作シミュレーションの検証では、従来比で電力効率10倍以上、起動時間10分の1以下の改善効果を確認しました。半導体回路設計環境の整備、車載やサーベイランスなどへの応用技術開発を進め、今後の半導体製品化とこれを実装したシステム製品の早期実現を通じて、世界のデファクトスタンダード化を目指します。

なお、2024年10月15日から10月18日まで幕張メッセで開催される「CEATEC 2024」開催期間中、NEDOブースで本成果を紹介します。

1.概要

NEDOは本事業※1に取り組んでおり、このたび、その成果が「CEATEC AWARD 2024」のネクストジェネレーション部門賞を受賞しました。

「CEATEC AWARD 2024」は、Society 5.0の総合展「CEATEC 2024」に展示される技術・製品・サービスの中から、出展者が事前に応募した出展品・案件について「CEATEC AWARD 2024 審査委員会」が審査・選考し、学術的・技術的観点や市場性、将来性などの点から、イノベーション性が高く優れていると評価できるものを表彰します。

今回受賞したのは、本事業の一環で3者が実施している世界に先駆けた「CMOS/スピントロニクス融合AI半導体」で、電力効率削減に繋がる研究開発を実施し、車載やサーベイランスをはじめ、さまざまな分野におけるエッジAIの活用に道を開いた点が評価されました。

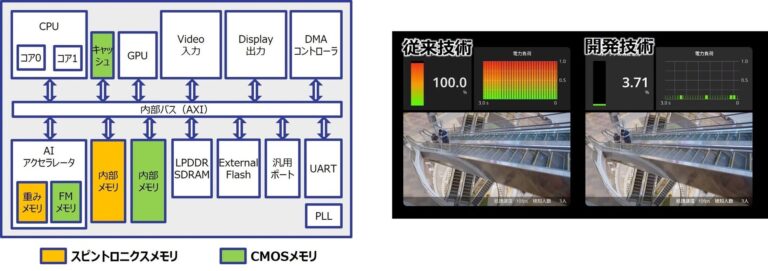

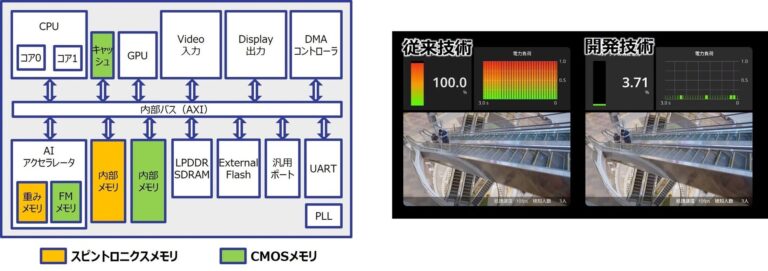

今回の成果では、CMOS/スピントロニクス融合技術※2を基盤とする大容量MRAM※3を、エッジ領域向けAI処理用半導体に搭載し、内部のAIアクセラレータ※4やプロセッサの周辺メモリとしてMRAMを配置して、MRAMの不揮発性と広帯域性を活用することにより、RTLでのシステム動作検証において、従来比で電力効率10倍以上および起動時間10分の1以下の改善効果を確認しました。

近年、情報処理に用いられるデバイスの高度化と、ネットワークのデータ量が爆発的に増加しているなか、エッジ領域におけるAI処理には電力やサイズ、インフラ環境などのさまざまな制約から、電力効率のよいAI半導体の重要性が増しています。これまでのAI半導体においては、CMOSデバイス技術を基盤としたメモリが搭載され、これを共用するようにシステムが構築されていました。本事業ではCMOS/スピントロニクスを基盤とするMRAMを採用して、その不揮発性と広帯域性を活用することにより、従来必要であったメモリ内容の保持に関する処理プロセスや動作時および待機時電力の削減、およびメモリを含むシステムの柔軟な構築を可能にしました。

今回設計した実証用チップでは、AIアクセラレータの重みメモリ※5と内部メモリの一部にMRAMを採用しました。これにより従来外付けFLASHメモリを用いてBOOT動作を行う際にかかっていたシステム起動時間の大幅短縮が可能となります。周辺部品削減によるシステムコスト削減に寄与するだけでなく、用途によっては非稼働時に電源を完全にオフにできることから、待機時電力を大幅に低減できると考えています。

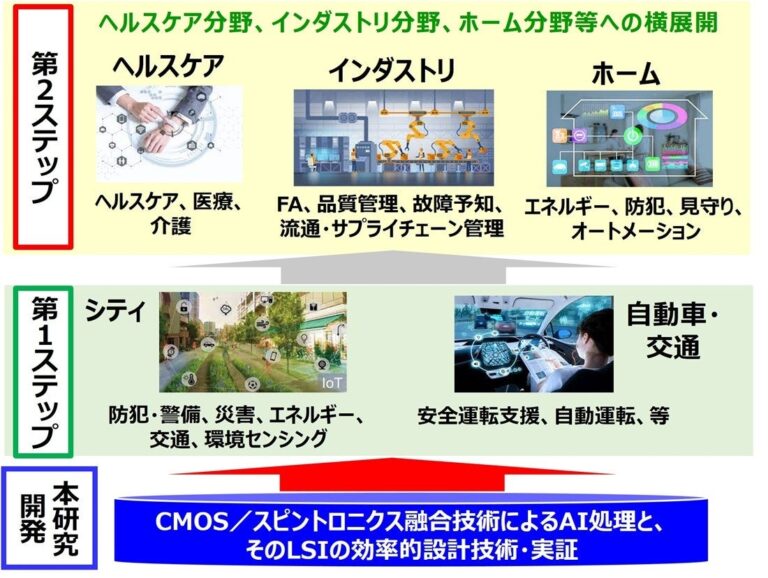

今後は、MRAMを搭載するAI半導体の回路設計手法を、より効率的にデバイス特性と連携できるよう整備し、車載やサーベイランスへの応用技術開発を行う予定です。その後、多くのAI企業による新事業創出、半導体製品化とこれを実装したシステム製品の早期実現を通じて、CMOS/スピントロニクス融合技術を基盤としたAI半導体のデファクトスタンダード化を目指します。

<受賞概要>

【ネクストジェネレーション部門賞】

受賞者:東北大学、NEC、アイシン

受賞案件:CMOS/スピントロニクス融合AI半導体

2.CEATEC 2024の開催概要

日時:2024年10月15日(火)~18日(金)

場所:幕張メッセ

主催:一般社団法人電子情報技術産業協会(JEITA)

なお、「CEATEC 2024」開催期間中、NEDOブースで本成果を紹介します。また、NEDOブースの出展内容の詳細は、以下のNEDOイベントページで紹介しています。

【注釈】

※1 本事業

事業名:省エネAI半導体及びシステムに関する技術開発事業/AIエッジコンピューティングの産業応用加速のための設計技術開発/CMOS/スピントロニクス融合技術によるAI処理半導体の設計効率化と実証、及び、その応用技術に関する研究開発

事業期間:2022年度~2024年度

※2 CMOS/スピントロニクス融合技術

技術開発が進むCMOS技術において極めて重要な問題となっている待機時電力をスピントロニクスの不揮発性を活用して大幅に削減し、加えてスピントロニクスの高い面積効率を活かし、スピントロニクス素子の微細化を通して電力効率10倍向上の実現を可能とする技術です。

※3 MRAM

MRAM(Magnetoresistive Random Access Memory)は、磁化の方向で情報を記憶する不揮発性メモリです。1ns程度の高速な磁化反転速度により高速動作が可能であるとともに、原子移動がないために書き換え耐性が高く、他の不揮発性メモリにはない優位性を有しています。

※4 AIアクセラレータ

AIアクセラレータとは、AIの計算処理を高速化するために設計されたハードウエアのことを指します。従来のCPUやGPUよりも高速にAIの計算を行い、AIアプリケーションにおけるコストを大幅に低減します。

※5 重みメモリ

重みメモリとは、ニューラルネットワークにおいて入力値の重要性、貢献度を数値化して表したものを格納するメモリのことです。ニューラルネットワークでは重みとバイアスを調整することで学習を進めます。バイアスは入力値を一定の範囲に偏らせるために用いるもので、重みはその入力値ごとに決められ、その入力値の価値を決めるもので推論や学習に使用されます。